浅析linux内核内存管理之PAE

作者:李万鹏

早期Intel处理器从80386到Pentium使用32位物理地址,理论上,这样可以访问4GB的RAM。然而,大型服务器需要大于4GB的RAM来同时运行数以千计的进程,近几年来这对Intel造成了压力,所以必须扩展32位80x86所支持的RAM容量。

Intel通过在它的处理器上把管脚数从32增加到36已经满足了这些需求,可以寻址64GB。同时引入了一种新的分页机制PAE(Physical Address Extension,物理地址扩展)把32位线性地址转换为36位物理地址才能使用所增加的物理内存,通过设置CR4的第5位来开启对PAE的支持。引入PAE就是为了访问大于4GB的RAM,线性地址仍然是32位,而物理地址是36位。

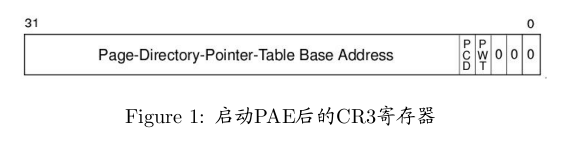

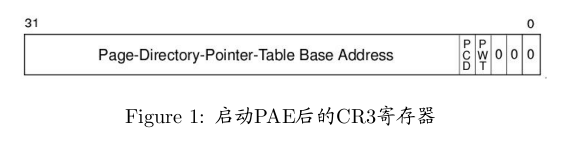

64GB的RAM被分为2^24个页框,页表项的物理地址字段从20位扩展到了24位。PAE表项必须包含12个标志位和24个物理地址位,总数之和为36,页表项大小从32位变为64位。这样原来一个页框有1024个entry,现在有512个entry。开启PAE的80x86 32位使用的是三级页表,第一级是新引入的PDPT(页目录指针表,相当于PGD了),第二级是PMD,第三级是PTE。PDPT只有4个entry,每个对应1GB RAM,每个entry 是64位。CR3中有27位作为PDPT的起始地址。

在开启PAE前,CR3中用20来存储页目录的起始地址;开启PAE后,用27位来存储page directory pointer table的起始地址。

下边分两种情况来讨论,一个是PS=0,一个是PS=1:

当CR4的第5位被置位(开启PAE),第4位被置位(开启PSE)

- 线性地址31~30,用来指向一个PDPT的entry

- 线性地址29~21,用来指向一个pmd的entry

- 线性地址20~0,为4MB大页中的offset

当CR4的第5位被置位(开启PAE),第4位被清除(关闭PSE)

- 线性地址31~30,用来指向一个PDPT的entry

- 线性地址29~21,用来指向一个pmd的entry

- 线性地址20~12,用来指向一个pte

- 线性地址11~0,为4KB页中的offset

如何访问64GB?

从上边的三级分页可以看到2^2*2^9*2^9*2^11=4GB,仍然访问的是4GB。访问64GB方法如下:

- 修改CR3中的值使其指向不同的PDPT,这样就指向不同的4GB

- 修改PDP entry中的值,使其指向不同的PMD表,这样可以指向不同的1GB

但是实际上是不能访问这么大的内存的,实际可用的内存被限制在16GB,因为如果有64GB,那么每个struct page结构需要32字节,总共512MB,这样ZONE_NORMAL的内核地址空间就被大量占用,这样是不允许的。

分享到:

相关推荐

Linux常见驱动源码分析(kernel hacker修炼之道)--李万鹏 李万鹏 IBM Linux Technology Center kernel team 驱动资料清单内容如下: Linux设备模型(中)之上层容器.pdf Linux设备模型(上)之底层模型.pdf Linux...

常见驱动源码分析( LINUX kernel hacker修炼之道)-李万鹏

常见驱动源码分析(kernel hacker修炼之道)

如果刚刚对linux的kernel有兴趣,想了解点什么的话,请先看看此书吧,她风趣幽默的介绍了linux的发展趣事,让你开心快乐之余慢慢领会linux的魅力,让你了解学习掌握kernel的方法。其中的很多建议经过我的实践和摸索...

国嵌的笔记 非常的不容易 里面驱动 包括USB LCD 文件系统 内存管理有非常详细 的记录

Linux PCI驱动牛人写的论文,有一定参考价值

有关hacker 的文章和资料分享给大家

渗透测试教程资料

Algorithm-HackerRank-Solutions-In-Scala.zip,在scala中解决hackerrank的挑战,算法是为计算机程序高效、彻底地完成任务而创建的一组详细的准则。

黑客入门教材,理论结合实践,通俗易懂。为读此书,先学英文也值得。

hacker-history.pdf hacker-history.pdf

HackerRank-Interview-Preparation-Kit-master.rar

rails-hackernews-reddit-producthunt-clone, 黑客 news/reddit/social 链接分享网站 用 Rails 构建 Rails 上的 Reddit-Hackernews-ProductHunt克隆演示 这是一个 readme.md的Ruby on Rails 应用程序,模仿了 Hacker...

Hacker 2012 - Final Transfer Readme =-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=-=- Thank you for downloading Hacker 2012! Registration ------------------------------------ If you like the game, ...

Process Hacker是一款功能丰富的系统程序,比windows自带的任务管理器功能更强大。用户只要借助该程序就可以方便,快捷地查看相关进程的速度,内存,及模块等等,除此,还可以对相关的进程进行管理工作。

Process Hacker是一款针对高级用户的安全分析工具,它可以帮助研究人员检测和解决软件或进程在特定操作系统环境下遇到的问题。除此之外,它还可以检测恶意进程,并告知我们这些恶意进程想要实现的功能。 Process ...

Resource Hacker 可以被用来: 1. 查看 Win32 可执行和相关文件的资源 (*.exe, *.dll, *.cpl, *.ocx),在已编译和反编译的格式下都可以。 2. 提取 (保存) 资源到文件 (*.res) 格式,作为二进制,或作为反编过的译...

Process Hacker是一款强大的系统进程管理工具,开源,并且还可以显示CPU、GPU、IO、内存等相关使用信息。 官网地址:https://processhacker.sourceforge.io/ git地址:...

Process Hacker是一款强大的系统进程管理工具,开源,并且还可以显示CPU、GPU、IO、内存等相关使用信息。 官网地址:https://processhacker.sourceforge.io/ git地址:...

前端开源库-esdoc-hacker-visionESDoc Hacker Vision,用于ESDoc的Hacker Vision前端插件