哈尔滨理工大学软件工程专业08-7李万鹏翻译作品,转载请标明出处

http://blog.csdn.net/woshixingaaa/archive/2011/03/16/6252330.aspx

文档整理自ARM System Developer's Guide

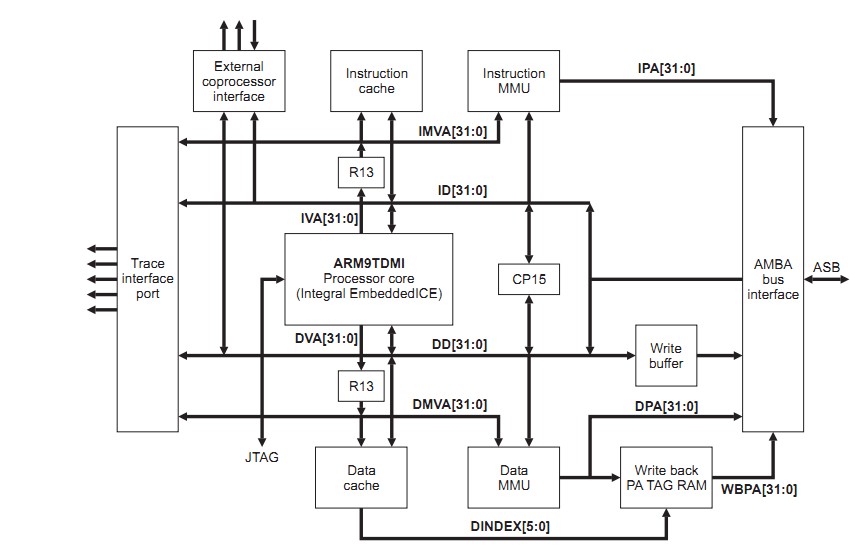

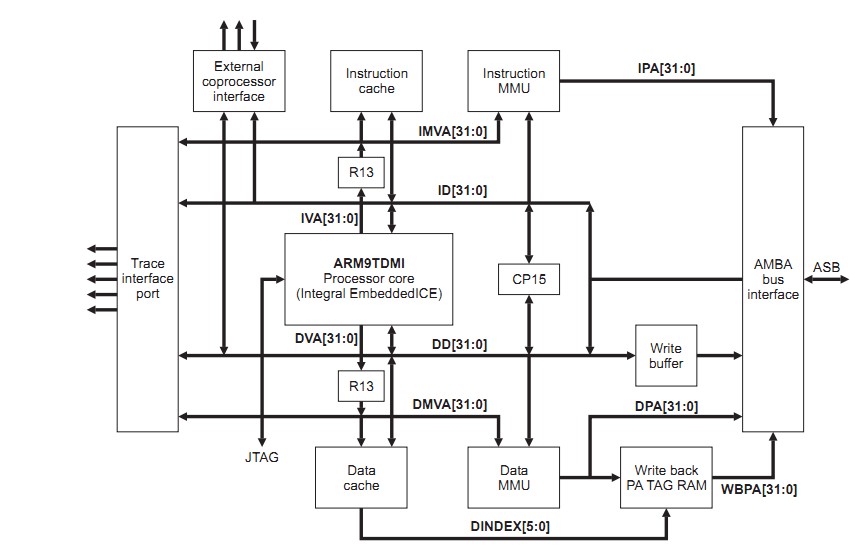

ARM920T处理器包含了ARM9TDMI内核,ARM9TDMI实现了ARM architecture v4T。

ARM920T处理器包含两个协处理器:

CP14。用于调试

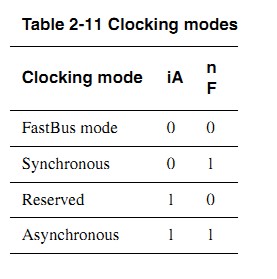

CP15。系统控制协处理器,提供附加的寄存器用来配置和控制cache,MMU,保护系统,时钟模式,和ARM920T其他的系统选项,如大小端操作。你可以使用MCR,MRC访问定义在CP15中的寄存器。

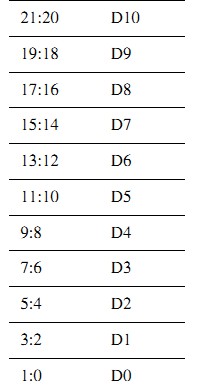

CP15定义了16个寄存器,寄存器的映射图如下:

注:寄存器位置0可以访问两个寄存器,通过opcode_2的值来确定。

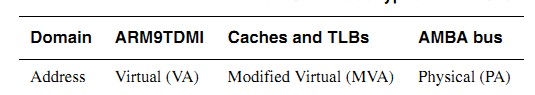

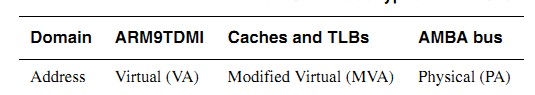

ARM920T存在3个地址。

只能在特权模式下使用MCR和MRC指令访问CP15。这些指令的格式是:

MCR/MRC{cond} P15,,Rd,CRn,CRm,

指令CDP,LDC,STC和非特权模式的MRC,MCR指令操作CP15会导致未定义指令异常。MRC和MCR指令的CRn域指定了要访问的协处理寄存器。opcode_1,和CRm域应该是0,除非值被指定用来选择需要的操作。

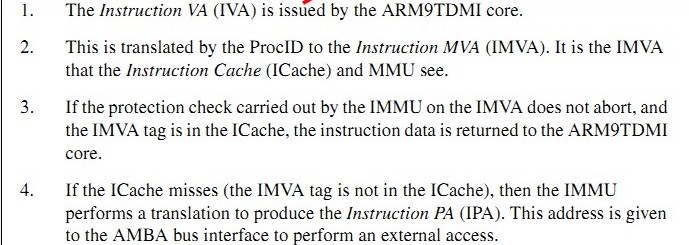

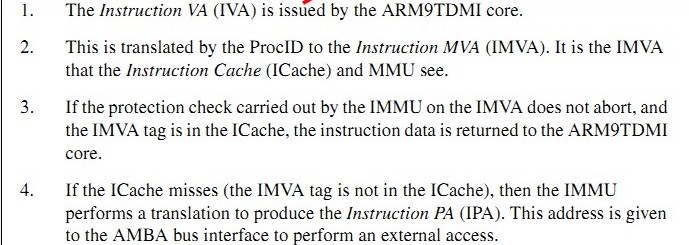

Register 0,ID code register

可以通过读CP15 register 0,opcode_2域设置成除了1的任何值(在读的时候CRm应该为0)。

如:

MRC p15,0,Rd,c0,c0,0;return ID register

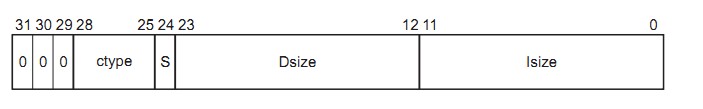

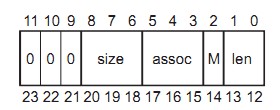

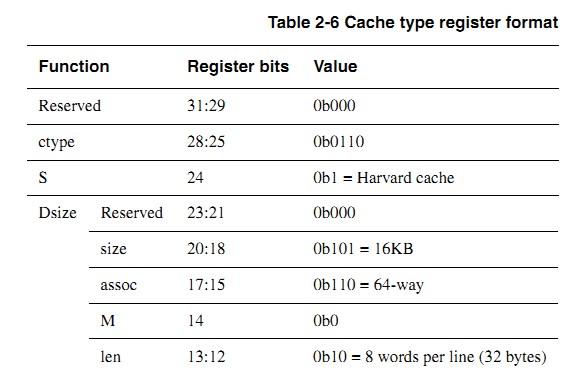

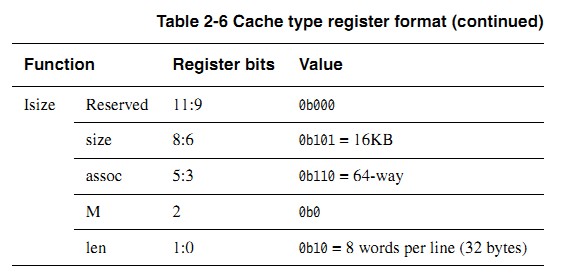

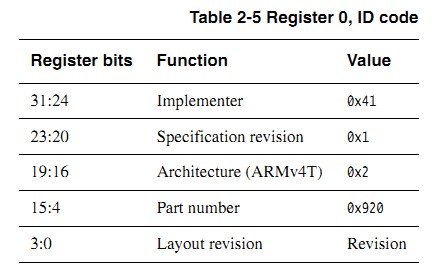

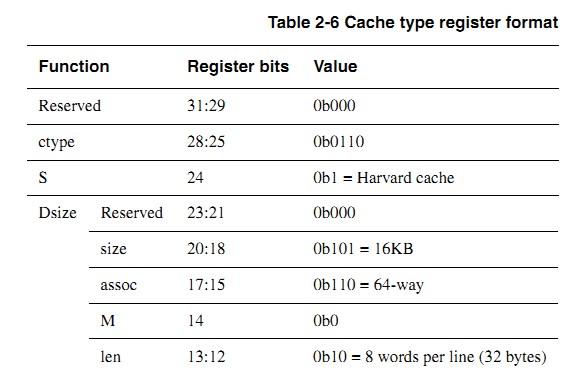

cache type register 0

包含cache的大小和体系结构的信息。可以通过设置域为1,读CP15 register 0来访问cache type register。例如:

MRC p15,0,Rd,c0,c0,1;returns cache details

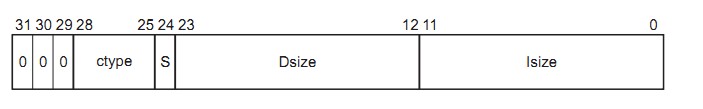

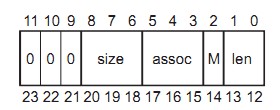

Dsize和Isize域格式一样:

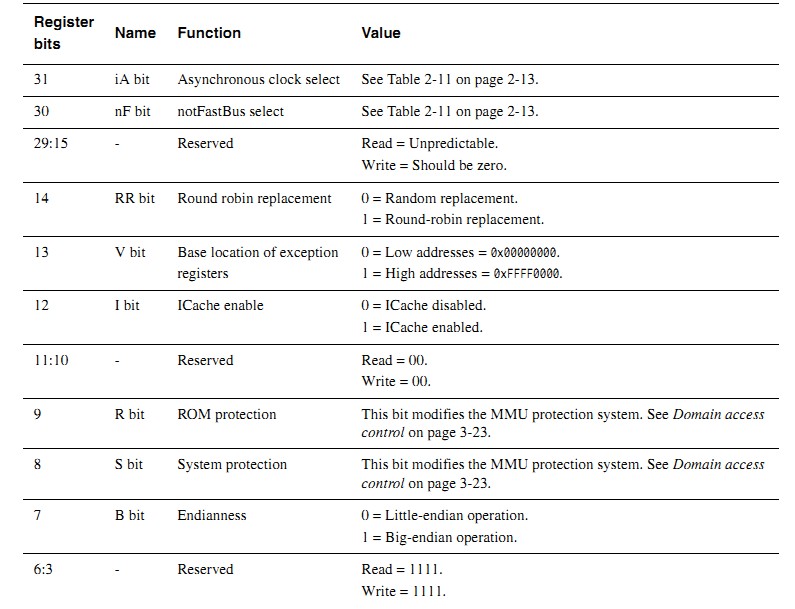

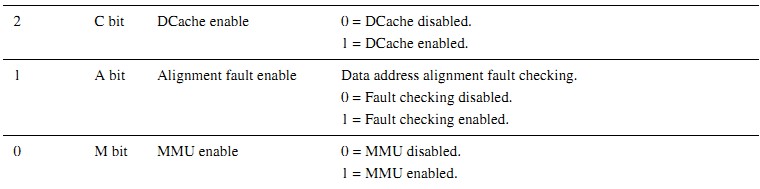

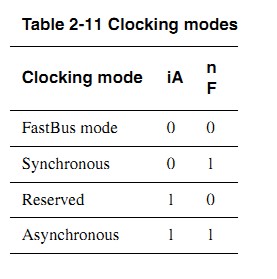

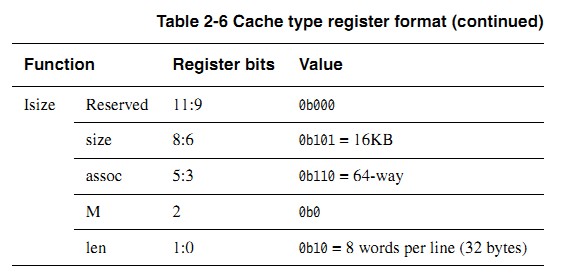

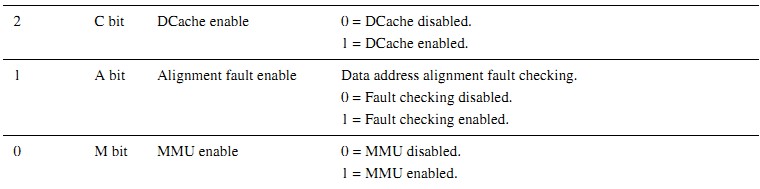

Register1,control register

这个寄存器包含了ARM920T的控制位。

MRC p15,0,Rd,c1,c0,0 ;read control register

MCR p15,0,Rd,c1,c0,0;write control register

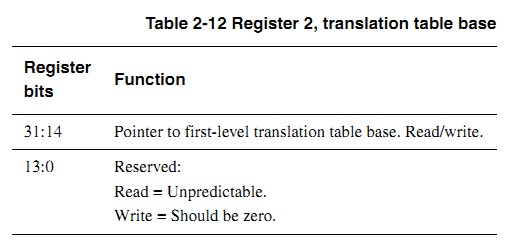

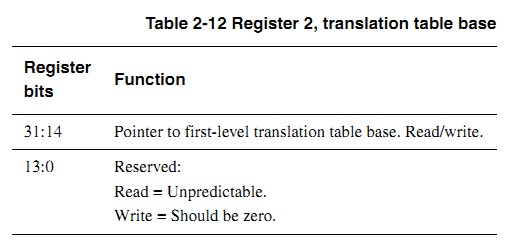

Register 2,translation table base(TTB)register

这个是页表基址寄存器。

使用下面的指令访问TTB:

MRC p15,0,Rd,c2,c0,0;read TTB register

MCR p15,0,Rd,c2,c0,0;write TTB register

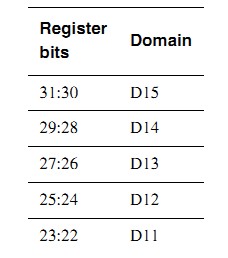

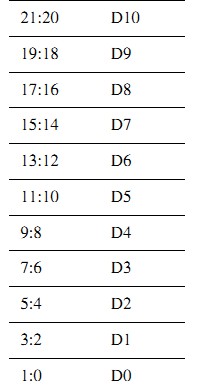

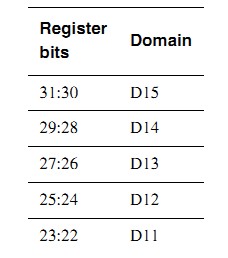

Register 3,domain access control register

这个是读写域访问控制寄存器。

MRC p15,0,Rd,c3,c0,0;read domain 15:0 access permissions

MCR p15,0,Rd,c3,c0,0;write domain 15:0 access permissions

Register 4,reserved

Register 5,fault status registers

Register 6,fault address registers

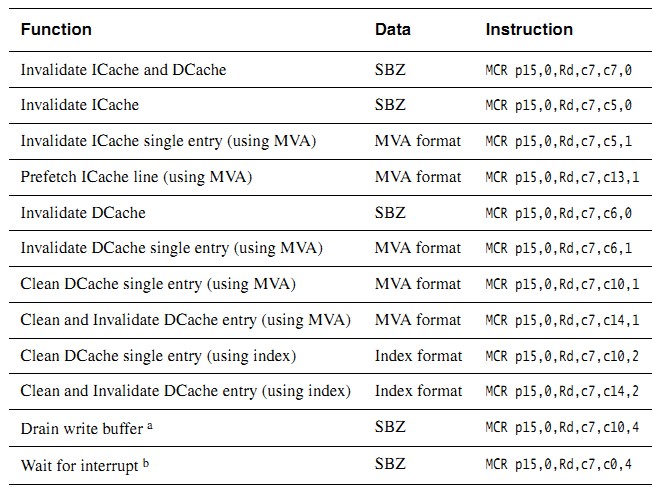

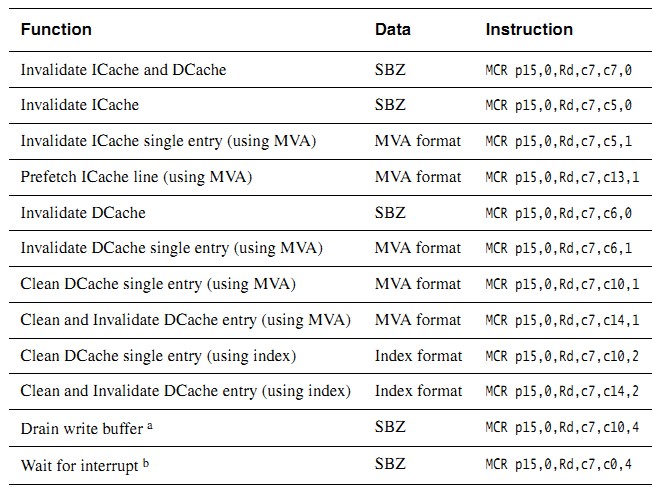

Register 7,cache operations register

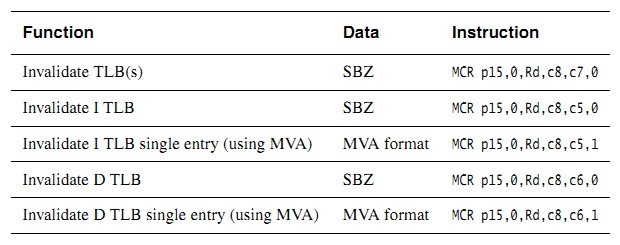

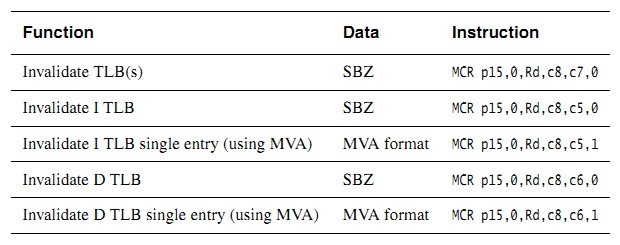

Register 8,TLB operations register

用来管理Translation Lookaside Buffers(TLBs),指令TLB和数据TLB。

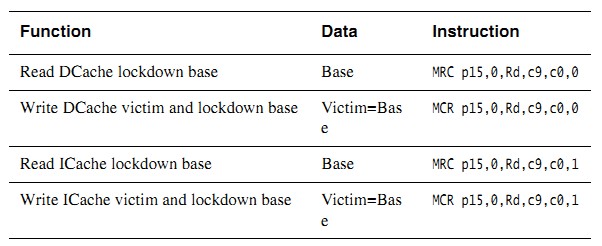

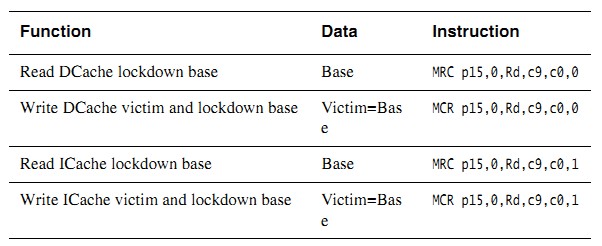

Register 9,cache lockdown register

opcode_2=0x0 访问的是Dcache

opcode_2=0x1 访问的是 Icache

Regiter 10,TLB lockdown register

opcode_2=0x0 访问的是D TLB

opcode_2=0x1 访问的是 I TLB

Register 11,12,and 14,reserved

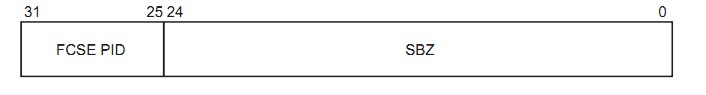

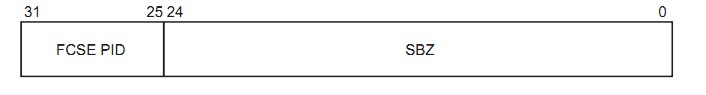

Register 13,FCSE PID register

是快速上下文切换扩展寄存器。

MRC p15,0,Rd,c13,c0,0;read FCSE_PID

MCR p15,0,Rd,c13,c0,0; write FCSE_PID

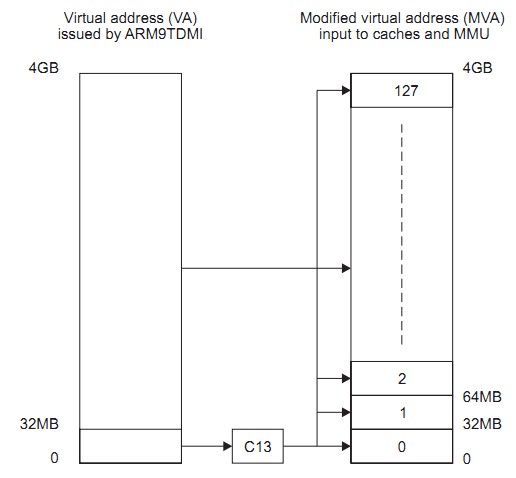

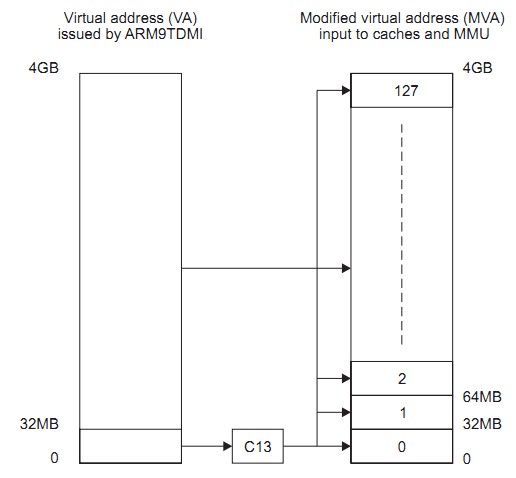

ARM9TDMI发出的地址在0~32MB范围内的被CP15的register 13转换。地址A变成A+(FCSE_PID×32MB)。FCSE_PID是一个7位的域,能够使128×32MB的进程被映射。

Register 15,test configuration register

分享到:

相关推荐

arm协处理器CP15详解

ARM920T Technical Reference Manual 这是一本全英文的ARM920T的手册

ARM920T内核技术手册ARM920T内核技术手册ARM920T内核技术手册ARM920T内核技术手册ARM920T内核技术手册ARM920T内核技术手册ARM920T内核技术手册

基于ARM920T的IDE硬盘接口设计

基于ARM920T微处理器的IDE硬盘接口设计与实现.pdf

本文详细介绍了ARM920T虚拟地址原理分析及实现,并引出了内存管理单元MMU的概念及其应用。比较适合那些对MMU不太了解的同学进行入门学习

对arm的协处理器15有比较深入的介绍,如果相对arm cpu有深层次的理解的话,可一看看

详细介绍 了arm920T的使用,包括如何安装,如何调试 如何使用,Linux下的编译器

ARM公司的官方资料,详细的介绍了ARM920T内核的各种细节,比市面上各种采用ARM920T为内核的嵌入式处理器的DS要详细的多

基于ARM920T的FLASH的读写 基于ARM920T的FLASH的读写

ARM9 ARM920T DataSheet说明书,详细讲述了ARM9内核结构

协处理器是一种芯片,用于减轻系统微处理器的特定处理任务。例如,数学协处理器可以控制数字处理;图形协处理器可以处理视频绘制。例如,intel pentium 微处理器就包括内置的数学协处理器。。。

绿色中文版Wince5.0模拟器arm920T

arm协处理器指令经常让人头疼,资料也不好找。这是我自己查阅众多资料后而成的arm协处理器指令解析,比较全希望对你有所帮助。

ARM920T Technical Reference Manual,ARM公司官方920T的说明文档。

ARM协处理器 ARM协处理器知识详细讲解了ARM协处理器

本文章介绍了ARM协处理器CP15的使用介绍,附带一个例子。 访问CP15寄存器指令的编码格式及语法说明如下: ······ 说明: <opcode>:协处理器行为操作码,对于CP15来说,永远为0b000,否则结果未知。 <rd>...